Page 40 - EngineerIT November 2021

P. 40

RADIO COMMUNICATION

In a slower FH mode with a sufficiently long transition time (greater

than the channel setup time and required PLL tuning time) between

frequency changes, only one PLL is needed for a pair of transmit and

receive channels in a TDD operation (PLL retune mode). To achieve faster

FH with a shorter transition time (shorter than the channel setup time

and required PLL tuning time), two PLLs are employed in the device (PLL

mux mode). The two PLLs coordinate with each other in a ping pong

fashion: while one PLL is used for the current frequency, the other PLL

is retuned to the next frequency. This makes very fast FH possible and

could significantly reduce the required transition time between different

frequency changes. These two modes are summarised in Table 1.

As shown in Table 1, the selection of these two modes depends on

the transition time the user defines.

Figure 4 further describes the concept of PLL mux mode. As

mentioned earlier, each time slot stands for a hop frame consisting of

a transition time period and a dwell time period. While one PLL is used

during the dwell time, the other PLL has started tuning from the beginning

of the transition time of the same hop frame. It can continue the tuning

until the end of the transition period of the next hop frame. Therefore, PLL

mux mode is successful as long as the required PLL tuning time is less than

the summation of one dwell time plus two transition times.

Figure 2: High-level block diagram of the ADRV9002 with flexible PLL design. FH with PLL mux mode is critical for military applications such

as Link 16, which is considered one of the most important tactical

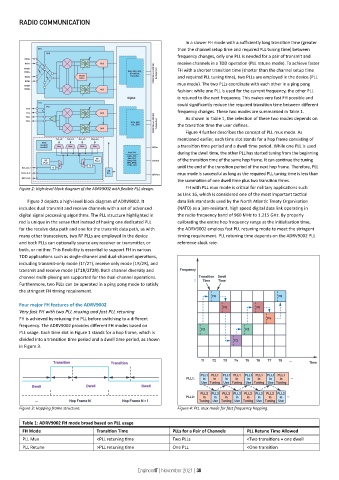

Figure 2 depicts a high-level block diagram of ADRV9002. It data link standards used by the North Atlantic Treaty Organisation

includes dual transmit and receive channels with a set of advanced (NATO) as a jam-resistant, high speed digital data link operating in

digital signal processing algorithms. The PLL structure highlighted in the radio frequency band of 960 MHz to 1.215 GHz. By properly

red is unique in the sense that instead of having one dedicated PLL calibrating the entire hop frequency range at the initialisation time,

for the receive data path and one for the transmit data path, as with the ADRV9002 employs fast PLL retuning mode to meet the stringent

many other transceivers, two RF PLLs are employed in the device timing requirement. PLL retuning time depends on the ADRV9002 PLL

and both PLLs can optionally source any receiver or transmitter, or reference clock rate.

both, or neither. This flexibility is essential to support FH in various

TDD applications such as single-channel and dual-channel operations,

including transmit-only mode (1T/2T), receive only mode (1R/2R), and

transmit and receive mode (1T1R/2T2R). Both channel diversity and

channel multi-plexing are supported for the dual-channel operations.

Furthermore, two PLLs can be operated in a ping pong mode to satisfy

the stringent FH timing requirement.

Four major FH features of the ADRV9002

Very fast FH with two PLL muxing and fast PLL retuning

FH is achieved by retuning the PLL before switching to a different

frequency. The ADRV9002 provides different FH modes based on

PLL usage. Each time slot in Figure 1 stands for a hop frame, which is

divided into a transition time period and a dwell time period, as shown

in Figure 3.

Figure 3: Hopping frame structure. Figure 4: PLL mux mode for fast frequency hopping.

Table 1: ADRV9002 FH mode broad based on PLL usage

FH Mode Transition Time PLLs for a Pair of Channels PLL Retune Time Allowed

PLL Mux <PLL retuning time Two PLLs <Two transitions + one dwell

PLL Retune >PLL retuning time One PLL <One transition

EngineerIT | November 2021 | 38