Page 18 - EngineerIT September 2021

P. 18

AUDIO PROCESSING

Figure 3: Analog Devices’ SigmaStudio graphical development

environment.

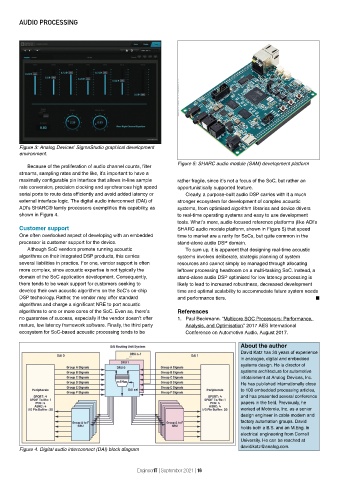

Figure 5: SHARC audio module (SAM) development platform

Because of the proliferation of audio channel counts, filter

streams, sampling rates and the like, it’s important to have a

maximally configurable pin interface that allows in-line sample rather fragile, since it’s not a focus of the SoC, but rather an

rate conversion, precision clocking and synchronous high speed opportunistically supported feature.

serial ports to route data efficiently and avoid added latency or Clearly, a purpose-built audio DSP carries with it a much

external interface logic. The digital audio interconnect (DAI) of stronger ecosystem for development of complex acoustic

ADI’s SHARC® family processors exemplifies this capability, as systems, from optimised algorithm libraries and device drivers

shown in Figure 4. to real-time operating systems and easy to use development

tools. What’s more, audio-focused reference platforms (like ADI’s

Customer support SHARC audio module platform, shown in Figure 5) that speed

One often overlooked aspect of developing with an embedded time to market are a rarity for SoCs, but quite common in the

processor is customer support for the device. stand-alone audio DSP domain.

Although SoC vendors promote running acoustic To sum up, it is apparent that designing real-time acoustic

algorithms on their integrated DSP products, this carries systems involves deliberate, strategic planning of system

several liabilities in practice. For one, vendor support is often resources and cannot simply be managed through allocating

more complex, since acoustic expertise is not typically the leftover processing headroom on a multi-tasking SoC. Instead, a

domain of the SoC application development. Consequently, stand-alone audio DSP optimised for low latency processing is

there tends to be weak support for customers seeking to likely to lead to increased robustness, decreased development

develop their own acoustic algorithms on the SoC’s on-chip time and optimal scalability to accommodate future system needs

DSP technology. Rather, the vendor may offer standard and performance tiers. n

algorithms and charge a significant NRE to port acoustic

algorithms to one or more cores of the SoC. Even so, there’s References

no guarantee of success, especially if the vendor doesn’t offer 1. Paul Beckmann. “Multicore SOC Processors: Performance,

mature, low latency framework software. Finally, the third party Analysis, and Optimisation.” 2017 AES International

ecosystem for SoC-based acoustic processing tends to be Conference on Automotive Audio, August 2017.

About the author

David Katz has 30 years of experience

in analogue, digital and embedded

systems design. He is director of

systems architecture for automotive

infotainment at Analog Devices, Inc.

He has published internationally close

to 100 embedded processing articles,

and has presented several conference

papers in the field. Previously, he

worked at Motorola, Inc. as a senior

design engineer in cable modem and

factory automation groups. David

holds both a B.S. and an M.Eng. in

electrical engineering from Cornell

University. He can be reached at

david.katz@analog.com.

Figure 4. Digital audio interconnect (DAI) block diagram

EngineerIT | September 2021 | 16