Page 27 - EngineerIT November 2021

P. 27

AUTOMATION AND CONTROL

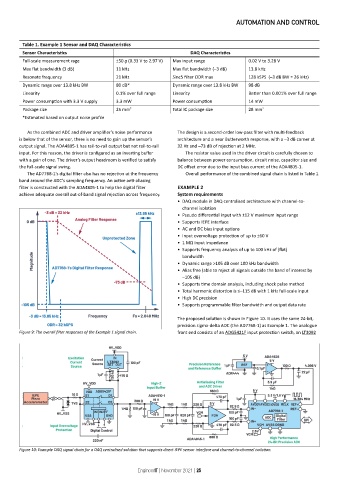

Table 1. Example 1 Sensor and DAQ Characteristics

Sensor Characteristics DAQ Characteristics

Full-scale measurement rage ±50 g (0.33 V to 2.97 V) Max input range 0.02 V to 3.28 V

Max flat bandwidth (3 dB) 11 kHz Max flat bandwidth (–3 dB) 13.8 kHz

Resonate frequency 21 kHz Sinc5 filter ODR max 128 kSPS (–3 dB BW = 26 kHz)

Dynamic range over 13.8 kHz BW 80 dB* Dynamic range over 13.8 kHz BW 98 dB

Linearity 0.1% over full range Linearity Better than 0.001% over full range

Power consumption with 3.3 V supply 3.3 mW Power consumption 14 mW

Package size 25 mm Total IC package size 28 mm 2

2

*Estimated based on output noise profile

As the combined ADC and driver amplifier’s noise performance The design is a second-order low-pass filter with multi-feedback

is below that of the sensor, there is no need to gain up the sensor’s architecture and a near Butterworth response, with a –3 dB corner at

output signal. The ADA4805-1 has rail-to-rail output but not rail-to-rail 32 Hz and –73 dB of rejection at 2 MHz.

input. For this reason, the driver is configured as an inverting buffer The resistor value used in the driver circuit is carefully chosen to

with a gain of one. The driver’s output headroom is verified to satisfy balance between power consumption, circuit noise, capacitor size and

the full-scale signal swing. DC offset error due to the input bias current of the ADA4805-1.

The AD7768-1’s digital filter also has no rejection at the frequency Overall performance of the combined signal chain is listed in Table 1.

band around the ADC’s sampling frequency. An active anti-aliasing

filter is constructed with the ADA4805-1 to help the digital filter EXAMPLE 2

achieve adequate overall out-of-band signal rejection across frequency. System requirements

• DAQ module in DAQ centralised architecture with channel-to-

channel isolation

• Pseudo differential input with ±12 V maximum input range

• Supports IEPE interface

• AC and DC bias input options

• Input overvoltage protection of up to ±60 V

• 1 MΩ input impedance

• Supports frequency analysis of up to 100 kHz of (flat)

bandwidth

• Dynamic range >105 dB over 100 kHz bandwidth

• Alias free (able to reject all signals outside the band of interest by

–105 dB)

• Supports time domain analysis, including shock pulse method

• Total harmonic distortion is ≤–115 dB with 1 kHz full-scale input

• High DC precision

• Supports programmable filter bandwidth and output data rate

The proposed solution is shown in Figure 10. It uses the same 24-bit,

precision sigma-delta ADC (the AD7768-1) as Example 1. The analogue

Figure 9: The overall filter responses of the Example 1 signal chain. front end consists of an ADG5421F input protection switch, an LT3092

Figure 10: Example DAQ signal chain for a DAQ centralised solution that supports direct IEPE sensor interface and channel-to-channel isolation.

EngineerIT | November 2021 | 25