Page 12 - EngineerIT June 2022

P. 12

ELECTRONICS

Figure 3: 2 x SPDT switch with extended protection.

The IC features internal positive overvoltage and surge protection. Figure 5: D+/D- eye diagram

The device handles USB low/full/high-speed signaling and

operates from a 2.7V to 5.5V supply. The IC is available in a Data Integrity

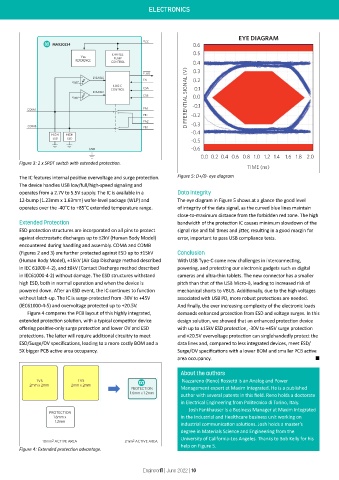

12-bump (1.23mm x 1.63mm) wafer-level package (WLP) and The eye diagram in Figure 5 shows at a glance the good level

operates over the -40°C to +85°C extended temperature range. of integrity of the data signal, as the curved blue lines maintain

close-to-maximum distance from the forbidden red zone. The high

Extended Protection bandwidth of the protection IC causes minimum slowdown of the

ESD protection structures are incorporated on all pins to protect signal rise and fall times and jitter, resulting in a good margin for

against electrostatic discharges up to ±2kV (Human Body Model) error, important to pass USB compliance tests.

encountered during handling and assembly. COMA and COMB

(Figures 2 and 3) are further protected against ESD up to ±15kV Conclusion

(Human Body Model), ±15kV (Air Gap Discharge method described With USB Type-C come new challenges in interconnecting,

in IEC 61000-4-2), and ±8kV (Contact Discharge method described powering, and protecting our electronic gadgets such as digital

in IEC61000-4-2) without damage. The ESD structures withstand cameras and ultra-thin tablets. The new connector has a smaller

high ESD, both in normal operation and when the device is pitch than that of the USB Micro-B, leading to increased risk of

powered down. After an ESD event, the IC continues to function mechanical shorts to VBUS. Additionally, due to the high voltages

without latch-up. The IC is surge-protected from -30V to +45V associated with USB PD, more robust protections are needed.

(IEC61000-4-5) and overvoltage protected up to +20.5V. And finally, the ever increasing complexity of the electronic loads

Figure 4 compares the PCB layout of this highly integrated, demands enhanced protection from ESD and voltage surges. In this

extended protection solution, with a typical competitor device design solution, we showed that an enhanced protection device

offering positive-only surge protection and lower OV and ESD with up to ±15kV ESD protection, -30V to +45V surge protection

protections. The latter will require additional circuitry to meet and +20.5V overvoltage protection can singlehandedly protect the

ESD/Surge/OV specifications, leading to a more costly BOM and a data lines and, compared to less integrated devices, meet ESD/

5X bigger PCB active area occupancy. Surge/OV specifications with a lower BOM and smaller PCB active

area occupancy. n

About the authors

Nazzareno (Reno) Rossetti is an Analog and Power

Management expert at Maxim Integrated. He is a published

author with several patents in this field. Reno holds a doctorate

in Electrical Engineering from Politecnico di Torino, Italy.

Josh Fankhauser is a Business Manager at Maxim Integrated

in the Industrial and Healthcare business unit working on

industrial communication solutions. Josh holds a master’s

degree in Materials Science and Engineering from the

University of California-Los Angeles. Thanks to Bob Kelly for his

help on Figure 5.

Figure 4: Extended protection advantage.

EngineerIT | June 2022 | 10