Page 17 - EngineerIT October 2022

P. 17

ELECTRONICS

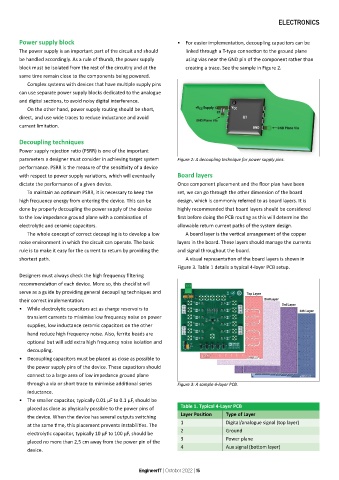

Power supply block • For easier implementation, decoupling capacitors can be

The power supply is an important part of the circuit and should linked through a T-type connection to the ground plane

be handled accordingly. As a rule of thumb, the power supply using vias near the GND pin of the component rather than

block must be isolated from the rest of the circuitry and at the creating a trace. See the sample in Figure 2.

same time remain close to the components being powered.

Complex systems with devices that have multiple supply pins

can use separate power supply blocks dedicated to the analogue

and digital sections, to avoid noisy digital interference.

On the other hand, power supply routing should be short,

direct, and use wide traces to reduce inductance and avoid

current limitation.

Decoupling techniques

Power supply rejection ratio (PSRR) is one of the important

parameters a designer must consider in achieving target system Figure 2: A decoupling technique for power supply pins.

performance. PSRR is the measure of the sensitivity of a device

with respect to power supply variations, which will eventually Board layers

dictate the performance of a given device. Once component placement and the floor plan have been

To maintain an optimum PSRR, it is necessary to keep the set, we can go through the other dimension of the board

high frequency energy from entering the device. This can be design, which is commonly referred to as board layers. It is

done by properly decoupling the power supply of the device highly recommended that board layers should be considered

to the low impedance ground plane with a combination of first before doing the PCB routing as this will determine the

electrolytic and ceramic capacitors. allowable return current paths of the system design.

The whole concept of correct decoupling is to develop a low A board layer is the vertical arrangement of the copper

noise environment in which the circuit can operate. The basic layers in the board. These layers should manage the currents

rule is to make it easy for the current to return by providing the and signal throughout the board.

shortest path. A visual representation of the board layers is shown in

Figure 3. Table 1 details a typical 4-layer PCB setup.

Designers must always check the high frequency filtering

recommendation of each device. More so, this checklist will

serve as a guide by providing general decoupling techniques and

their correct implementation:

• While electrolytic capacitors act as charge reservoirs to

transient currents to minimise low frequency noise on power

supplies, low inductance ceramic capacitors on the other

hand reduce high frequency noise. Also, ferrite beads are

optional but will add extra high frequency noise isolation and

decoupling.

• Decoupling capacitors must be placed as close as possible to

the power supply pins of the device. These capacitors should

connect to a large area of low impedance ground plane

through a via or short trace to minimise additional series Figure 3: A sample 4-layer PCB.

inductance.

• The smaller capacitor, typically 0.01 μF to 0.1 μF, should be

placed as close as physically possible to the power pins of Table 1. Typical 4-Layer PCB

the device. When the device has several outputs switching Layer Position Type of Layer

1 Digital/analogue signal (top layer)

at the same time, this placement prevents instabilities. The

electrolytic capacitor, typically 10 μF to 100 μF, should be 2 Ground

3 Power plane

placed no more than 2,5 cm away from the power pin of the

device. 4 Aux signal (bottom layer)

EngineerIT | October 2022 | 15